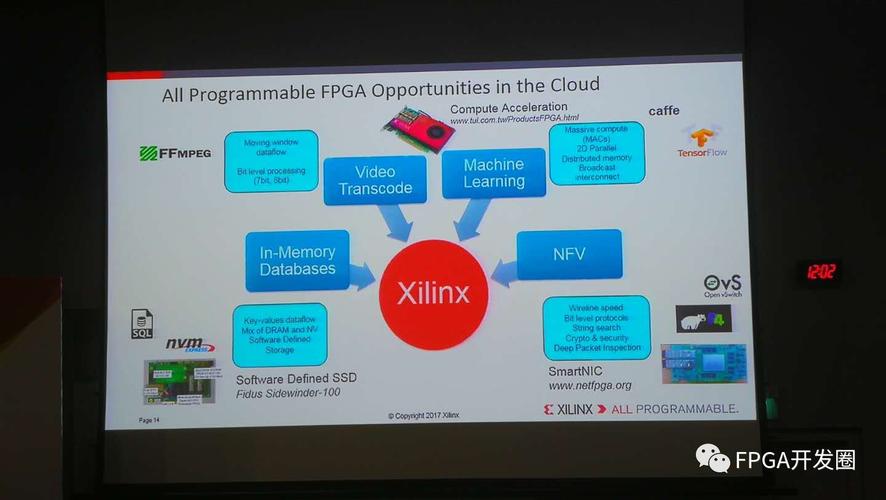

这是一个由赛灵思公司(现已被AMD收购)提出并大力推广的核心理念和市场营销术语,它旨在描述一种现代数字系统设计的范式,强调其设计的灵活性、可扩展性和生命周期价值。

“All Programmable”技术指的是利用FPGA(现场可编程门阵列)以及相关的SoC(片上系统)和MPSoC(多处理器片上系统)技术,来实现从底层硬件逻辑到上层软件应用的全流程可编程性。

下面我们从几个层面来深入理解这个技术。

核心思想:为什么需要“All Programmable”?

传统的数字系统设计主要有两种路径:

- 专用集成电路:为特定功能量身定制的芯片,优点是性能最高、功耗最低、成本在大批量时最低,缺点是开发周期长、前期投入巨大(NRE费用高)、设计完成后无法修改,一旦芯片流片失败或需要更新,代价极其高昂。

- CPU/GPU等处理器:通过软件指令来执行计算,优点是极其灵活,软件可以随时更新,缺点是执行效率相对较低,因为它们是基于冯·诺依曼架构的“顺序执行”模型,对于高度并行化的任务,其性能远不及硬件逻辑。

“All Programmable”技术的出现,正是为了融合这两种范式的优点,同时规避其缺点。

它提供了一个“黄金分割点”:

- 像ASIC一样高效:你可以根据需求,在FPGA内部直接“编程”出专用的硬件逻辑(如数据通路、滤波器、加密引擎等),实现接近ASIC的并行处理能力和低延迟。

- 像CPU一样灵活:这些硬件逻辑不是固化在硅片上的,而是可以通过代码(如HDL硬件描述语言或HLS高层次综合工具)进行配置和修改,你还可以在FPGA中嵌入处理器核心(如ARM Cortex-A/R),运行操作系统和上层软件,实现软硬件的协同工作。

核心组件:实现“All Programmable”的关键技术

赛灵思(AMD)通过其产品线,将“All Programmable”理念具体化:

-

FPGA (现场可编程门阵列)

- 基础:这是“All Programmable”的基石,FPGA内部由大量的可配置逻辑块、输入输出单元和可编程互连组成。

- 可编程性:用户通过加载不同的“比特流”文件,就可以重新配置这些逻辑块和互连,从而实现完全不同的数字电路功能,这是实现底层硬件可编程的关键。

-

SoC / MPSoC (片上系统 / 多处理器片上系统)

(图片来源网络,侵删)

(图片来源网络,侵删)- 融合:这是“All Programmable”理念的升华,赛灵思将处理器(如ARM Cortex-A53应用处理器、Cortex-R5实时处理器)与FPGA逻辑 fabric 集成到同一块芯片上。

- 协同工作:

- ARM处理器:运行Linux、Android等操作系统,处理控制、界面、网络通信等复杂任务。

- FPGA逻辑:作为可编程加速器,负责处理算法密集型、高带宽、低延迟的任务(如视频编解码、AI推理、雷达信号处理)。

- 优势:实现了“软硬件协同设计”,开发者可以根据应用需求,将最合适的任务分配给处理器或硬件逻辑,达到性能、功耗和灵活性的最佳平衡。

-

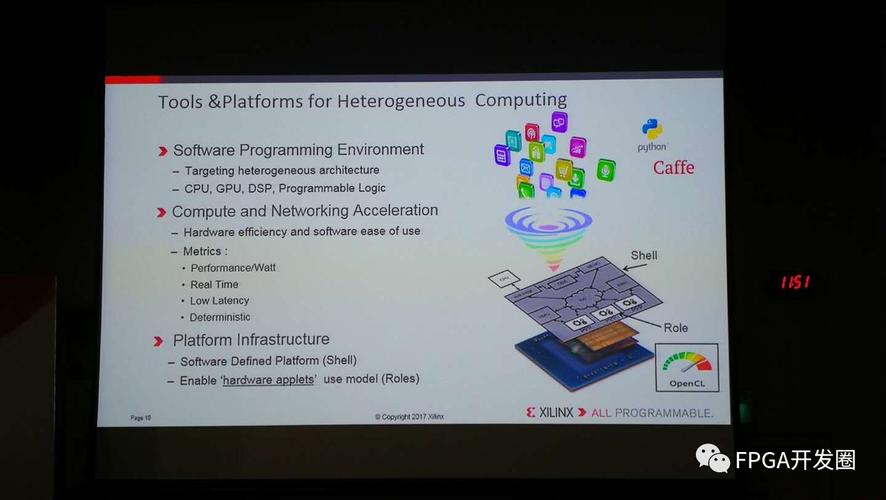

工具链:Vivado / Vitis

- 设计平台:没有强大的工具链,“All Programmable”就是空谈,AMD的Vivado设计套件和Vitis统一软件平台是实现这一理念的核心。

- Vivado:专注于FPGA和SoC的逻辑设计,支持HDL(Verilog/VHDL)和HLS(高层次综合),可以将C/C++/SystemC代码直接转换为硬件电路。

- Vitis:这是一个统一软件平台,它将软件编程(C/C++/Python)和硬件编程无缝集成在一起,开发者可以使用同一套工具链、同一套API,为MPSoC中的处理器核和可编程逻辑分别编写和优化代码,极大地降低了开发门槛。

主要优势与特点

- 灵活性:这是最核心的优势,产品可以在设计后期甚至上市后,通过更新比特流来增加新功能、修复漏洞或升级算法,这是ASIC无法比拟的。

- 高性能与低延迟:通过定制硬件逻辑实现并行计算,处理速度远超通用处理器,特别适合实时应用。

- 快速上市时间:相比于ASIC长达数年的开发周期,基于FPGA的原型验证和产品开发周期大大缩短,能快速响应市场需求。

- 长期产品支持:对于生命周期很长的产品(如工业、航空航天、国防领域),FPGA的可重配置性意味着可以在不更换硬件的情况下,支持产品运行十数年甚至更久,避免了芯片停产的风险。

- 软硬件协同优化:开发者可以根据应用特性,将任务在软件和硬件之间进行最优化分配,实现“恰到好处”的性能和功耗,而不是过度设计。

- 降低系统总成本:在某些应用中,使用一颗高性能的MPSoC可能比使用一颗CPU + 一颗ASIC的组合方案成本更低,功耗也更优。

典型应用领域

“All Programmable”技术因其独特优势,在以下领域得到了广泛应用:

- 5G通信:基站中的前传、中传、回传处理,需要极高的灵活性和实时性来应对不断演进的通信标准(如4G到5G的平滑过渡)。

- 数据中心与云计算:用于网络功能虚拟化、软件定义网络、AI推理和训练的硬件加速,提升服务器效率和能效比。

- 汽车电子:高级驾驶辅助系统、自动驾驶域控制器、车载信息娱乐系统,需要处理来自多个传感器的海量数据,且对功能安全和实时性要求极高。

- 工业自动化:机器视觉、工业机器人、PLC(可编程逻辑控制器)等,需要高可靠性和实时控制能力。

- 航空航天与国防:软件定义无线电、雷达/电子战系统、加密通信,这些领域要求设备能快速适应新的威胁和通信标准,且生命周期极长。

- 人工智能与边缘计算:在终端设备(如摄像头、无人机)上实现本地化的AI推理,需要低延迟、高能效的硬件加速。

挑战与未来趋势

尽管优势明显,“All Programmable”技术也面临一些挑战:

- 开发门槛高:传统的FPGA开发需要掌握硬件描述语言,对硬件工程师要求较高,虽然HLS和Vitis等工具在努力降低门槛,但与软件开发的易用性相比仍有差距。

- 设计复杂性:软硬件协同设计比单纯的硬件或软件设计更复杂,需要开发者具备跨领域的知识。

- 成本与功耗:相比于成熟的ASIC或低功耗的MCU,高性能FPGA的单元成本和静态功耗仍然较高。

未来趋势:

- 更高层次的抽象:通过AI辅助设计、高级综合和C++/Python等高级语言的直接支持,让更多软件背景的工程师能够使用FPGA。

- 与AI的深度融合:利用AI技术来自动优化FPGA布局布线,加速FPGA本身的开发过程。

- 异构计算平台:将FPGA与CPU、GPU、NPU等更多类型的计算单元集成在一起,构建更强大的异构计算平台,满足AI时代对算力的多样化需求。

- 安全性增强:随着应用越来越关键,FPGA的安全启动、比特流加密、硬件级安全隔离等功能将变得愈发重要。

“All Programmable”技术并非指某一种单一技术,而是一种以FPGA/MPSoC为硬件载体,以软硬件协同设计为核心方法,以灵活性、高性能、快速迭代**为目标的现代数字系统设计哲学和方法论,它为应对当今快速变化、应用日益复杂的市场需求,提供了一个强大而富有弹性的解决方案,是推动数字化转型和智能化升级的关键使能技术之一。