fd soi技术是什么

fd soi技术,全称为全耗尽绝缘体上硅(Fully Depleted Silicon On Insulator)技术,是一种先进的半导体制造工艺,通过在硅晶圆与底层衬底之间引入一层绝缘层(通常是二氧化硅),并对顶层硅膜进行完全耗尽设计,实现了比传统体硅工艺更优异的电气性能和功耗表现,该技术起源于20世纪80年代的 soi 技术,但通过优化硅膜厚度和掺杂浓度,解决了早期 soi 技术存在的短沟道效应抑制不足、驱动能力较弱等问题,成为高性能、低功耗芯片制造的关键解决方案之一。

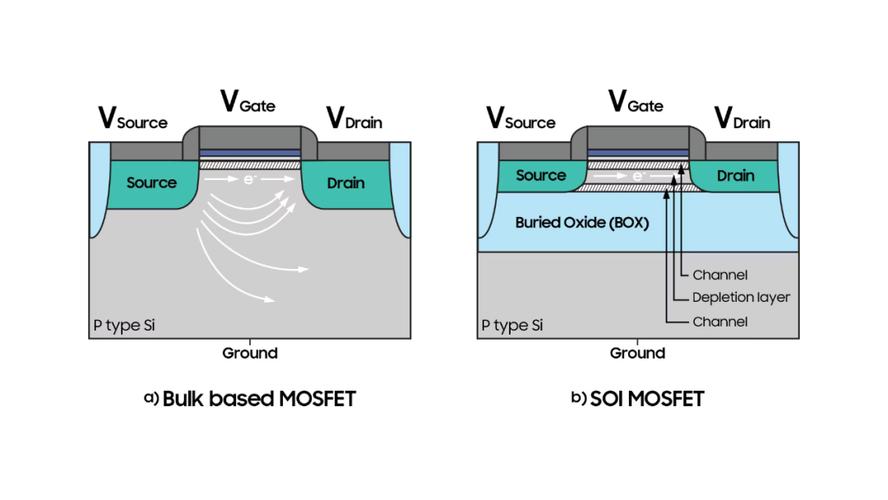

从结构上看,fd soi 晶圆主要由三层组成:顶层是厚度极薄(通常为几纳米至几十纳米)的单晶硅层,作为晶体管的沟道区域;中间是埋氧层(buried oxide layer,box),厚度一般为几十纳米至几百纳米,具有极高的绝缘性能,可有效隔离顶层硅与底层衬底;底层是硅衬底,作为晶圆的机械支撑体,与部分耗尽 soi(pd soi)技术不同,fd soi 技术的顶层硅膜在零偏压或工作偏压下即可被耗尽,整个硅膜内不存在电荷积累区域,这使得晶体管的沟道电势被埋氧层和衬底共同控制,从而大幅提升了器件的短沟道效应抑制能力。

fd soi 技术的核心优势在于其独特的“体偏置”(body bias)能力,由于顶层硅膜与衬底之间被埋氧层完全隔离,可以通过在硅膜背面施加电压(back bias),动态调节晶体管的阈值电压,在需要高性能的场景下,施加正向体偏置可降低阈值电压,提高开关速度;在待机或低负载场景下,施加负向体偏置可提高阈值电压,有效抑制漏电流,实现功耗的精细化控制,这种动态电压调节能力,使得基于 fd soi 技术的芯片能够在性能与功耗之间灵活切换,特别适用于移动设备、物联网终端等对能效比要求严苛的应用场景。

在性能方面,fd soi 技术显著提升了晶体管的开关速度和驱动能力,由于埋氧层消除了体硅中的寄生 pn 结电容,晶体管的寄生电容大幅降低,使得信号传输延迟减少,工作频率得以提高,薄硅膜设计增强了栅极对沟道的控制能力,减少了漏电流和亚阈值摆幅,进一步提升了器件的开关比,实验数据显示,与相同工艺节点的体硅器件相比,fd soi 器件的漏电流可降低2-3个数量级,功耗降低30%-50%,而速度提升约15%-20%。

fd soi 技术的另一个重要优势是抗辐射能力,埋氧层能有效阻挡高能粒子辐射,减少辐射引起的电荷泄漏和单粒子翻转效应,该特性使其成为航空航天、军事电子等特殊领域芯片的理想选择,fd soi 晶圆制造过程中无需额外的深槽隔离工艺,芯片面积可缩小约20%,进一步降低了制造成本。

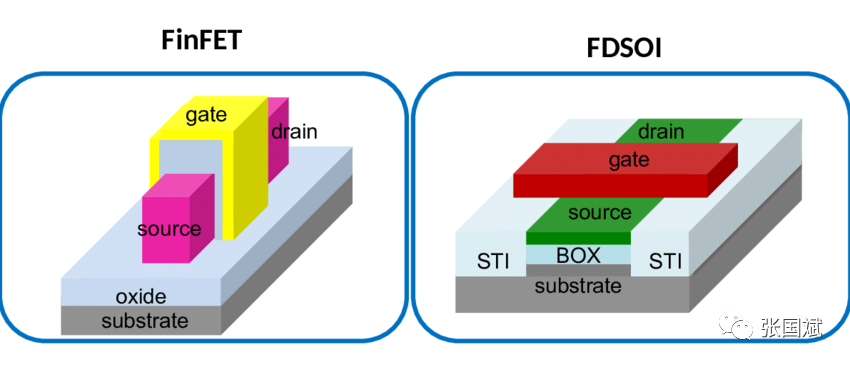

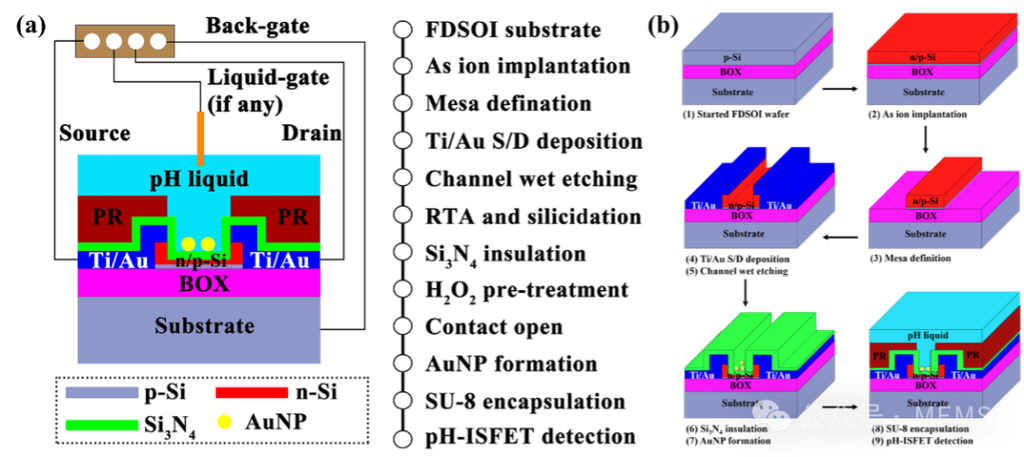

fd soi 技术的制造流程主要包括以下几个关键步骤:通过离子注入或注氧隔离(simox)技术在硅衬底中形成埋氧层;通过外延生长或化学机械抛光(cmp)技术控制顶层硅膜的厚度,确保其满足全耗尽条件;采用传统的光刻、刻蚀、掺杂等工艺制造晶体管结构;通过背面减薄和背面金属化工艺实现体偏置电极的制备,与 finfet 等三维结构技术相比,fd soi 技术的制造工艺与现有体硅生产线兼容性更高,可降低设备投资和改造成本,尤其适合对成本敏感的中低工艺节点(如28nm及以上)芯片生产。

fd soi 技术的应用领域广泛,在移动通信领域,智能手机的应用处理器、基带芯片采用 fd soi 技术后,可在保证性能的同时延长电池续航时间;在物联网领域,低功耗传感器节点、可穿戴设备芯片通过 fd soi 技术实现了超低待机功耗;在汽车电子领域,fd soi 技术的高可靠性和抗干扰能力满足车规级芯片的严苛要求;在射频前端领域,fd soi 技术的高Q值无源器件和低噪声特性,有助于提升5G通信模块的性能。

尽管 fd soi 技术具有诸多优势,但其发展也面临一些挑战,薄硅膜厚度的均匀性控制难度较大,易导致器件性能波动;埋氧层的缺陷密度可能影响芯片的长期可靠性;随着工艺节点向更先进制程(如7nm及以下)推进,fd soi 技术在短沟道效应抑制方面可能需要与 finfet、gaa 等技术结合使用,这些问题通过工艺优化和材料创新正在逐步解决,例如采用高k金属栅极、硅膜应力工程等技术进一步提升 fd soi 器件性能。

| 特性指标 | fd soi 技术 | 传统体硅技术 |

|---|---|---|

| 漏电流 | 低(10⁻¹⁵ a/μm 量级) | 高(10⁻¹² a/μm 量级) |

| 功耗降低 | 30%-50% | 基准 |

| 开关速度提升 | 15%-20% | 基准 |

| 抗辐射能力 | 优秀(埋氧层隔离) | 较差 |

| 芯片面积缩小 | 约20% | 基准 |

| 制造成本 | 较低(兼容现有产线) | 基准 |

相关问答FAQs:

-

问:fd soi 技术与 finfet 技术相比,各有什么优缺点?

答:fd soi 技术的优势在于工艺兼容性高、制造成本较低,且通过体偏置实现动态功耗控制,特别适合中低工艺节点的低功耗应用;而 finfet 技术采用三维结构,在短沟道效应抑制方面更具优势,更适合7nm及以下先进制程,fd soi 技术的缺点是在极小工艺节点下,沟道控制能力可能弱于 finfet;finfet 的缺点是制造工艺复杂,成本较高,且动态功耗调节灵活性不如 fd soi。 -

问:fd soi 技术是否适用于高性能计算芯片?

答:fd soi 技术在部分高性能计算场景中具有应用潜力,尤其是在对能效比要求较高的领域(如移动计算、边缘服务器),但由于其驱动能力和频率提升空间有限,在顶级高性能计算芯片(如cpu、gpu)中,finfet 或 gaa 技术仍是主流选择,fd soi 技术可能与这些先进技术结合,例如在 finfet 结构中引入 soi 衬底,以兼顾性能与功耗优化。