集成电路与系统设计技术是现代信息社会的核心驱动力,它涵盖了从器件物理、电路设计到系统集成、验证测试的全流程技术体系,是支撑人工智能、5G通信、物联网、自动驾驶等前沿领域发展的基石,随着摩尔定律逐步逼近物理极限,集成电路与系统设计技术正从单纯的“尺寸缩小”向“系统级创新”与“异构集成”演进,通过多学科交叉融合,不断突破性能、功耗与成本的瓶颈。

核心技术构成与演进趋势

集成电路与系统设计技术以半导体物理为基础,结合计算机体系结构、EDA(电子设计自动化)工具、制造工艺等多学科知识,形成层次化的技术体系,其核心构成包括:

- 器件与工艺技术:从早期的MOSFET到FinFET、GAA(环绕栅极)晶体管,晶体管结构不断优化以缩短沟道长度、抑制漏电流,当前,3nm及以下工艺节点采用纳米片(Nanosheet)晶体管,配合EUV(极紫外光刻)技术,实现晶体管密度与性能的持续提升,新材料如二维材料(如MoS₂)、宽禁带半导体(如GaN、SiC)的应用,为高频、高压场景提供了新的解决方案。

- 数字电路设计:基于硬件描述语言(如Verilog、VHDL)的RTL(寄存器传输级)设计仍是主流,通过逻辑综合、布局布线等流程转化为物理版图,随着SoC(片上系统)复杂度突破百亿晶体管,低功耗设计(如电源门控、动态电压频率调节)、可测试性设计(如扫描链、内建自测试)成为关键,近年来,RISC-V等开源指令集架构的兴起,推动了处理器IP核的模块化与定制化设计。

- 模拟与混合信号电路设计:在传感器、射频前端等场景中,模拟电路负责信号采集与调理,其设计需兼顾精度、速度与功耗,高速ADC/DAC、低噪声放大器、锁相环等模块的设计依赖于工艺模型与经验参数,是模拟电路设计的难点,随着Chiplet(小芯片)技术的兴起,芯粒间的高速互连(如UCIe标准)成为混合信号集成的重要方向。

- 系统级设计与验证:从RTL级到系统级,需通过SystemC、UVM(统一验证方法论)等工具进行功能验证与性能评估,针对AI加速器、自动驾驶芯片等复杂系统,异构计算架构(CPU+GPU+FPGA+AI专用核)的设计成为主流,通过任务调度与资源优化实现能效比最大化,硬件安全设计(如可信执行环境、物理不可克隆函数)日益受到重视,以应对侧信道攻击等安全威胁。

关键挑战与创新方向

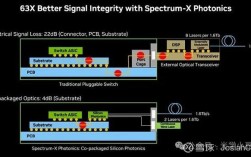

- 摩尔定律的延续与超越:当传统CMOS工艺逼近量子极限,三维集成(如TSV硅通孔)、先进封装(如2.5D/3D封装)成为延续摩尔定律的关键路径,通过将不同工艺节点、不同功能的芯粒集成在同一封装内,实现“超越摩尔”的系统级性能提升。

- EDA工具的智能化升级:面对设计复杂度的指数级增长,传统EDA工具已难以满足需求,基于AI/ML的EDA技术(如布局布线优化、时序分析)正逐步成熟,通过深度学习算法加速设计收敛,降低人力成本,谷歌的AlphaFold已在蛋白质折叠中展现AI潜力,未来有望应用于电路布局优化。

- 异构集成与协同设计:数字、模拟、射频、存储等不同功能模块的协同设计成为系统级优化的核心,通过统一设计语言(如SystemVerilog)与跨层验证方法,实现信号完整性、电源完整性、电磁兼容性的协同优化,芯粒间的互连标准(如BoW、HBM)与封装散热技术(如液冷、均热板)需同步发展。

- 软硬件协同设计:为应对特定场景(如边缘计算、实时处理)的需求,硬件架构需与算法深度适配,针对Transformer模型的稀疏性,AI芯片采用稀疏化计算单元;针对自动驾驶的实时性需求,采用“CPU+ASIC”异构架构,通过软件定义硬件功能。

典型应用场景

集成电路与系统设计技术的创新驱动了多领域的技术突破:

- 人工智能:GPU、TPU、NPU等AI加速芯片通过大规模并行计算与低精度量化(如INT4、INT8),实现大模型的高效推理,NVIDIA的H100 GPU采用台积电4N工艺,集成800亿晶体管,支持Transformer引擎加速。

- 5G/6G通信:射频前端芯片(如5G PA、滤波器)采用GaN/SiC材料提升功率效率;基带芯片通过毫米波技术实现高速率传输,同时支持Massive MIMO与波束赋形。

- 物联网:低功耗微控制器(如ARM Cortex-M系列)结合传感器融合技术,实现智能穿戴设备、工业传感器的长续航与高精度感知。

- 汽车电子:自动驾驶芯片(如NVIDIA Orin、地平线征程6)集成CPU+GPU+AI核,支持多传感器数据融合;车规级芯片需通过AEC-Q100认证,满足-40℃~125℃工作温度要求。

相关问答FAQs

Q1:集成电路设计中的“功耗墙”问题如何解决?

A:功耗墙是指芯片功耗密度过高导致散热困难,限制性能提升的问题,解决方案包括:①采用低功耗设计技术,如动态电压频率调节(DVFS)、时钟门控;②引入新型器件材料,如二维材料晶体管降低漏电;③通过异构集成将高性能核与低功耗核结合,根据任务负载动态调度;④优化电源管理单元(PMU),实现多级电压域精细化控制。

Q2:Chiplet技术如何推动集成电路产业发展?

A:Chiplet技术通过将复杂系统拆分为多个功能独立的芯粒,采用先进封装(如CoWoS、InFO)集成,具有三大优势:①降低成本:不同芯粒可采用最优工艺节点(如AI芯粒用7nm,I/O芯粒用28nm),避免全芯片使用先进工艺的高昂费用;②提升良率:单个芯粒面积小,缺陷率更低,整体系统良率提升;③加速迭代:可独立升级芯粒(如更新AI计算核),无需重新设计整个系统,AMD的Ryzen处理器采用Chiplet架构,将CPU核心与I/O模块分离,实现性能与成本的最优平衡。