Intel封装技术是连接芯片制造与实际应用的关键桥梁,其发展历程不仅推动了半导体性能的突破,更重新定义了芯片设计的边界,从早期的DIP封装到如今的Foveros、EMIB等先进技术,Intel通过不断创新的封装工艺,实现了更高集成度、更低功耗和更强性能,为计算、人工智能、数据中心等领域提供了核心支撑。

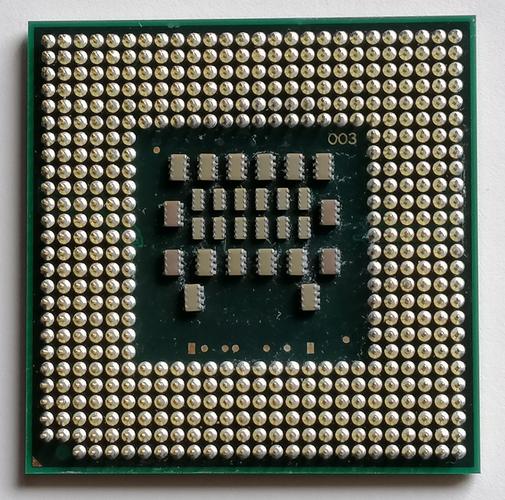

早期的Intel封装技术主要围绕基础电气连接和物理保护展开,20世纪70年代,双列直插封装(DIP)成为主流,通过引脚插入电路板实现固定,但体积较大且布线复杂,随着芯片集成度提升,Intel引入了球栅阵列封装(BGA),将引脚替换为焊球阵列,大幅提升了封装密度和散热性能,这一技术至今仍在移动处理器和显卡中被广泛应用,进入21世纪,芯片多核化趋势加速,Intel推出扇出型封装(FO),通过将芯片引脚延伸到封装体之外,减少了信号传输距离,提高了高频信号完整性,为处理器性能提升奠定了基础。

近年来,Intel封装技术进入“异构集成”新阶段,通过将不同工艺、不同功能的芯片在封装层进行三维堆叠,突破传统单芯片性能瓶颈,2025年,Intel发布Foveros技术,这是业界首款3D堆叠封装方案,在逻辑芯片上方直接堆叠存储芯片或I/O芯片,通过微米级硅通孔(TSV)实现垂直互连,使芯片面积缩小45%的同时,功耗降低30%,Foveros技术最初应用于移动处理器,后续扩展至高性能计算领域,如Lakefield混合架构处理器便通过Foveros将10nm核心与22nm低功耗核心集成,实现了性能与能效的平衡。

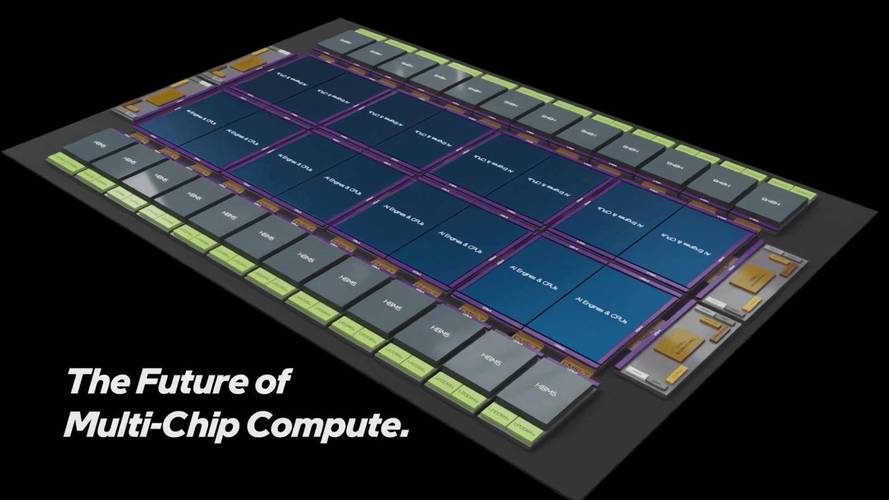

2025年,Intel进一步推出EMIB(嵌入式多芯片互连桥接)技术,通过在封装基板上嵌入微型硅桥连接不同芯片,解决了3D堆叠中高成本和良率问题,相较于Foveros的全堆叠方案,EMIB成本更低且灵活性更高,例如Intel Agilex FPGA芯片便利用EMIB将逻辑芯片与高带宽内存芯片集成,显著提升了数据处理能力,Intel还结合了Co-EMIB技术,将多个EMIB桥接组合,实现更复杂的多芯片互连,为数据中心级芯片设计提供了可能。

在先进封装材料与散热方面,Intel同样走在行业前列,其采用的高介电常数低k介质材料,有效降低了信号传输过程中的延迟和串扰;而硅通孔(TSV)技术则通过垂直金属互连,缩短了芯片间信号路径,使数据传输速率提升50%以上,针对高功率芯片的散热需求,Intel开发了嵌入式散热通道(Embedded Cooling Channels),在封装层直接集成微流冷却管道,配合液冷技术可降低芯片温度达20℃,为高密度计算提供了可靠保障。

Intel封装技术将继续向“芯粒化(Chiplet)”和“系统级封装(SiP)”方向发展,通过将不同功能的芯粒(如CPU、GPU、AI加速器)标准化,并利用先进封装技术灵活组合,可大幅降低芯片设计成本,加速产品迭代,Intel正在研发的“X-Pack”封装平台,将进一步整合光互连技术,解决芯片间高速数据传输的瓶颈,为下一代计算架构奠定基础。

相关问答FAQs

Q1:Intel的Foveros技术和EMIB技术有何区别?

A1:Foveros是3D堆叠封装技术,通过在逻辑芯片上方直接堆叠其他芯片,实现垂直集成,适合高密度集成场景;EMIB则是2.5D封装技术,通过在封装基板上嵌入硅桥连接不同芯片,成本更低且灵活性更高,适合多芯片互连但无需堆叠的场景,两者结合可满足不同芯片设计的集成需求。

Q2:先进封装技术对芯片性能有哪些具体提升?

A2:先进封装技术通过缩短信号传输路径(如TSV技术)、提升集成密度(如Foveros堆叠)和优化散热设计(如微流冷却),可显著降低延迟、提高带宽(最高提升50%)、减少功耗(降低30%以上),并支持异构芯片集成,使芯片整体性能和能效比得到跨越式提升。