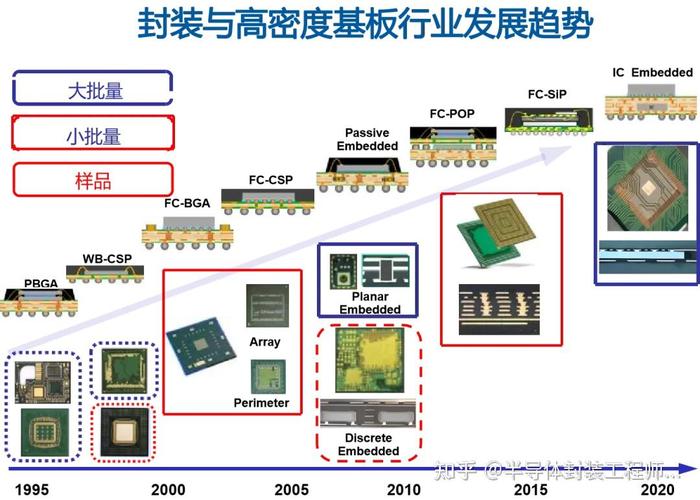

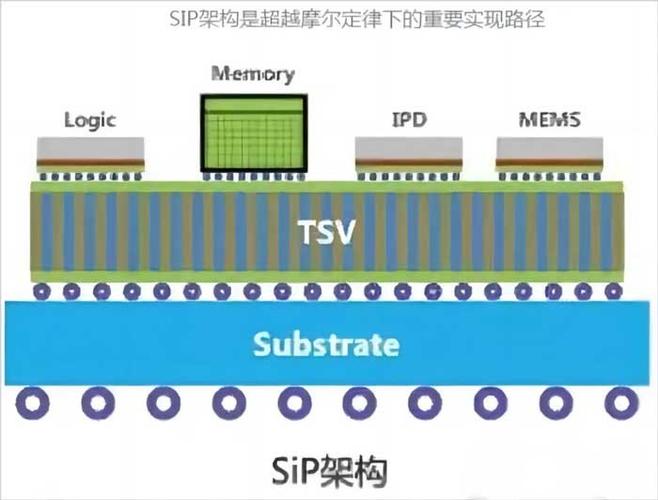

SIP 技术的核心思想是 “More than Moore”(超越摩尔定律),它不是单纯地追求芯片线宽的缩小,而是通过先进封装技术,在有限的空间内实现更高的系统性能、更低的功耗和更小的尺寸。

下面我将从 技术原理、关键制造工艺、主要技术路线、挑战与未来趋势 四个方面,为您全面解析 SIP 系统封装制造技术。

SIP 技术概述:为什么需要 SIP?

在 SIP 出现之前,电子系统的构建方式是:

- 分别制造不同功能的芯片(逻辑、存储、模拟、射频等)。

- 将每个芯片独立封装成单个组件。

- 在印刷电路板上将这些封装好的芯片通过焊接(如 BGA)连接起来。

这种方式存在诸多问题:

- 尺寸大: 芯片之间有 PCB 走线和封装占位,整体体积庞大。

- 性能低: 芯片之间的连接距离长,信号传输延迟高,带宽受限。

- 功耗高: 长距离传输和多次转换会消耗更多能量。

- 成本高: 多个独立封装和 PCB 组装流程增加了成本。

SIP 应运而生,它将上述多个芯片和无源元件“堆叠”或“并排”地集成在一个封装基板上,形成一个类似“芯片级系统”的模块。

SIP 的核心制造技术

SIP 的制造是一个高度集成的过程,涉及半导体和封装两大领域的尖端技术,其核心制造技术可以分为以下几个关键步骤:

芯片准备

这是制造的第一步,目的是为后续的集成提供“积木”。

- 减薄: 将芯片的厚度从几百微米减薄到几十微米甚至更薄,便于堆叠和散热。

- 切割: 将晶圆上的单个芯片切割下来,现在更先进的是 “先切割后封装”,即先将晶圆切割成独立的芯片,再进行后续的堆叠和封装,这样可以提高良率。

- 芯粒: 这是当前最前沿的方向,不再使用完整的芯片,而是将一个大型芯片(如 CPU)切割成多个更小的、功能完整的芯粒,这些芯粒可以作为“超级积木”进行集成,极大提高了制造的灵活性和良率。

先进封装基板

封装基板是 SIP 的“骨架”,它为芯片提供电气连接、机械支撑和散热通道。

- 材料: 传统的 FR-4 材料已无法满足 SIP 的高密度、高频、高速需求,现在普遍使用的是 ABF(Build-up Film,积层膜) 基板,它具有更高的布线密度、更好的信号完整性和更低的介电常数。

- 制造工艺: 采用类似 PCB 的积层法,通过反复叠加绝缘层和铜箔,并使用激光钻孔形成微小的导通孔,从而实现高密度的布线。

芯片堆叠与互连技术

这是 SIP 制造的核心,决定了系统的集成度和性能。

- .5D 封装:

- 原理: 将多个芯片并排放置在一个 中介层 上,中介层是一个硅基板,上面有极其密集的硅通孔,用于连接芯片之间的信号。

- 制造: 芯片通过 微凸块 倒装焊接到中介层上,中介层再通过 焊球 连接到封装基板。

- 特点: 芯片之间通过中介层的超短互连,大大缩短了信号路径,解决了“内存墙”问题,代表产品是 AMD 的 CPU/GPU 集成方案。

- 3D 封装:

- 原理: 将芯片在垂直方向上进行堆叠,像搭积木一样。

- 制造: 主要通过 硅通孔 技术实现,TSV 是在芯片制造过程中,直接在硅片上刻蚀出的垂直深孔,然后用金属(通常是铜)填充,形成贯穿芯片的电气连接。

- 特点: 实现了最高程度的集成,功耗和延迟最低,广泛用于高带宽存储器,如 HBM(High Bandwidth Memory),HBM 就是将多层 DRAM 芯片通过 TSV 堆叠在一起,并通过一个基板与 GPU 连接。

- 混合键合:

- 原理: 这是 3D 封装的终极形态,它不再使用微凸块,而是直接将两个芯片的晶圆进行 “铜-铜” 或 “硅-硅” 的直接键合。

- 制造: 需要极高的平整度和超洁净的环境,通过在原子级别实现直接共价键合,形成电气和机械连接。

- 特点: 互连密度极高、间距极小(可达微米甚至纳米级)、散热性能好、外形更薄,是未来 Chiplet(芯粒)集成的主流技术。

无源元件集成

SIP 的一个重要优势是能将电阻、电容、电感等无源元件也集成进去。

- 嵌入式无源元件: 在封装基板的制造过程中,将无源材料(如高介电常数陶瓷)嵌入到基板的内层,形成电容;或将电阻材料嵌入形成电阻。

- 薄膜无源元件: 在芯片或基板表面通过物理/化学气相沉积等技术溅射一层薄膜,然后通过光刻和蚀刻制成无源元件。

- 优点: 节省 PCB 空间、减少寄生参数、提高系统高频性能。

封装与测试

- 底部填充: 在芯片和基板之间的缝隙中填充环氧树脂,提高机械强度和可靠性,防止因热膨胀系数不匹配导致的开裂。

- 塑封: 使用环氧树脂模塑料将整个芯片和基板包裹起来,提供物理保护和环境隔离。

- 凸块制作与植球: 在封装基板的底部制作焊球,以便将其焊接在主板上。

- 电性测试和可靠性测试: 对封装好的 SIP 模块进行全面的电气性能测试,以及高低温循环、振动、跌落等可靠性测试。

主要技术路线对比

| 技术路线 | 结构特点 | 优点 | 缺点 | 典型应用 |

|---|---|---|---|---|

| 5D 封装 | 芯片平铺在中介层上 | 解决长距离互连,性能提升显著 | 中介层成本高,制造复杂 | 高性能计算、AI加速卡、CPU/GPU 集成 |

| 3D TSV 封装 | 芯片垂直堆叠,通过 TSV 互连 | 集成度最高,延迟和功耗最低 | TSV 工艺复杂,成本极高,良率挑战大 | 高带宽内存、图像传感器、手机 SoC |

| 混合键合 | 芯片直接原子级键合 | 互连密度和性能极致,外形超薄 | 技术门槛最高,工艺控制难度极大 | AI、HPC 的 Chiplet 集成 |

| PiP/PoP 封装 | 封装内的堆叠(如内存堆叠在处理器封装上) | 成本相对较低,技术成熟 | 集成度和性能提升有限 | 智能手机、移动设备 |

挑战与未来趋势

挑战:

- 热管理: 高度集成导致功率密度急剧增加,热量难以散发,是 SIP 面临的最大挑战之一。

- 信号完整性: 高频信号在密集互连中容易产生串扰、衰减等问题,对设计和制造精度要求极高。

- 良率与成本: 工艺步骤繁多,任何一个环节出现问题都会导致整个模块报废,良率控制是降低成本的关键。

- 异质集成: 如何将不同材料(硅、砷化镓、玻璃)、不同工艺(逻辑、存储、MEMS)的芯片完美地集成在一起,是技术和设计上的巨大挑战。

- 测试与验证: 集成度的提高使得故障定位和测试变得异常困难。

未来趋势:

- Chiplet(芯粒)化: 这是 SIP 未来的绝对主流,将大型 SoC 拆分为功能明确的芯粒,通过先进封装(如 2.5D/3D/混合键合)进行“乐高式”组合,这不仅能提高性能、降低成本,还能实现不同工艺节点的最优组合。

- 异构集成平台化: 将 SIP 封装本身打造成一个标准化的平台,允许客户像搭积木一样选择不同的芯粒进行定制化组合,加速产品上市。

- 新材料的应用: 采用更低介电常数的封装材料、高导热的界面材料、硅光子材料等,来解决信号和散热瓶颈。

- AI 驱动的 EDA 和制造: 利用人工智能进行芯片设计、封装仿真和制造过程控制,以应对日益增长的复杂性。

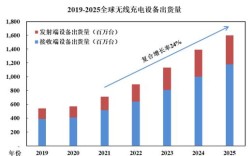

- 超越封装的系统集成: SIP 将进一步与天线、传感器、执行器等结合,实现真正的“系统级”集成,在物联网、可穿戴设备、自动驾驶等领域发挥巨大作用。

SIP 系统封装制造技术是后摩尔时代半导体产业发展的核心驱动力,它通过 5D、3D TSV、混合键合 等先进工艺,将不同功能的芯片和无源元件高效地集成在一个微小的封装体内,实现了性能、功耗和尺寸的完美平衡,虽然面临热管理、良率等诸多挑战,但随着 Chiplet(芯粒) 概念的兴起和新材料的不断应用,SIP 必将在人工智能、5G/6G、高性能计算等下一代信息技术领域扮演不可或缺的关键角色。